Artificial Intelligence (AI) is rapidly expanding beyond digital environments and into the physical world. AI-driven systems that give machines the ability to perceive, comprehend, learn from, and respond to real-time environments are quickly moving from imagination to reality. Training and inference models are expanding rapidly, complex Systems on Chip (SoCs) are processing information at increasing speeds, and vision and sensor applications are creating a new generation of edge, industrial, and automotive solutions that interact more closely with the physical world. As customers design new products geared for physical AI, Cadence is building a chiplet ecosystem and collaborating with Samsung Foundry to build a platform prototype using Samsung’s SF5A process technology.

Why chiplets matter for physical AI

Traditional monolithic SoCs are hitting physical limits: routing density, thermal budgets, and the reticle area limitations. Chiplets—individual functional blocks fabricated separately and later integrated at the package level—offer several advantages:

- Heterogeneous integration – Combine best-in-class analog, digital, and AI compute technologies without compromising each block’s performance.

- Scalable design – Reuse validated chiplets across multiple products, reducing development time dramatically.

- Power efficiency – Tailor voltage and frequency per chiplet, an essential capability for battery-powered edge devices.

- Yield and cost balance – Use smaller dies to improve manufacturing yield and lower per-unit cost, enabling large-scale deployment of physical AI-based applications.

- Compute density – Tile multiple AI-focused chiplets (matrix engines, Tensor cores) to reach the TOPS needed for real-time perception, sensor fusion, and reinforcement learning inference.

- Cross-application versatility – Serve data center accelerators, robotics, industrial IoT, automotive ADAS, and consumer AR/VR headsets all with the same architecture.

Physical AI workloads, such as real-time vision processing on a camera module, AI-enhanced radar in autonomous vehicles, smart manufacturing equipment, and sensor‑based systems, directly benefit from the advantages of chiplet architectures.

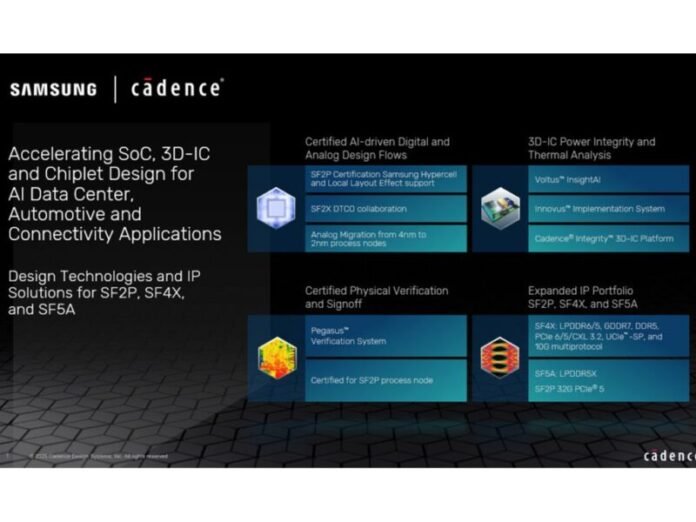

The collaboration

Cadence’s Chiplet Spec‑to‑Packaged‑Parts ecosystem streamlines engineering and shortens time to market for chiplet‑based solutions across the physical AI, data center, and high‑performance computing (HPC) markets. Samsung Foundry is co-developing a silicon prototype of the Cadence physical AI chiplet platform, integrating pre-verified partner IP implemented on Samsung’s SF5A process technology.

“We’re pleased to collaborate with Cadence to demonstrate the competitiveness of Samsung’s SF5A technology,” said Taejoong Song, Vice President of Foundry Technology Planning, Samsung Electronics. “Through this trusted partnership, we look forward to the successful expansion of the Chiplet Spec-to-Packaged-Parts ecosystem and helping customers accelerate reliable paths to cutting-edge silicon solutions for physical AI applications, including next-generation automotive designs.”

![]()

Samsung Foundry provides automotive-grade process technologies ranging from 14nm down to advanced 2nm nodes, and the SF5A node was selected for this project. Our automotive processes are AG2 qualified, and our design methodology incorporates AEC-Q100-aware signoff, design for test (DFT), and zero DPPM practices, as well as advanced functional safety support. In addition, the readiness of our design infrastructure, together with extensive design collateral and foundational IP, further accelerates the path to silicon success.

Looking ahead

The Samsung Foundry and Cadence collaboration, as a part of the Spec-to-Packaged-Parts ecosystem, is turning the promise of physical AI into tangible silicon. The pre-verified platform:

- Reduces design time by supplying a ready-to-use foundation

- Lowers development risk with proven IP and process-verified building blocks

- Offers flexible heterogeneous integration of chiplets for a wide range of physical AI workloads—from edge-vision systems to next-generation automotive ADAS

Together, Samsung Foundry’s robust process technology and Cadence’s comprehensive chiplet ecosystem are helping enable a scalable, secure, and performance‑driven foundation for the upcoming wave of physical AI systems. As the industry continues to shift toward multi‑die, chiplet-based architectures, this joint effort helps accelerate customer innovation across data center, robotics, automotive, and consumer domains.